-

Verilog2C++ translates a C++ class of a Verilog design using a cycle-accurate

representation of each nets and registers.

Verilog2C++ is about 10 times faster than other commercial simulators,

but has only simple functions.

- Support for IEEE1364-2001

- Only two sate simulation

- Static scheduled and cycle based simulation

- Not include the simulation kernel

- Not support system tasks

- Not support initial and task statement

-

Download a

"Verilog2C++.tgz"

|

>tar zxvf Verilog2C++.tgz >cd Verilog2C++ >make >make install >cd .. |

- file_name : Verilog source

- module_name : Top level module

- port_name : Synchronous port

|

Verilog2C++ file_name module_name

[posedge port_name]

[negedge port_name]

[comments]

[dumpvars]

|

-

Download a

"Sample.tgz"

|

>tar zxvf Sample.tgz >cd Sample |

"UDIV64.v2k" is written in Verilog-2001 as module UDIV64.

|

>Verilog2C++ UDIV64.v2k UDIV64 posedge CLK negedge RSTn |

A C++ test bench "bench.cc" is created manually from a Verilog test bench "bench.v" .

|

>g++ -O3 bench.cc UDIV64.cc -o simc >./simc |

If you have a Icarus Verilog.

|

>v2v UDIV64.v2k > UDIV64.v >iverilog bench.v UDIV64.v -o simv >./simv |

If you have a VCS.

|

>vcs +2state +v2k bench.v UDIV64.v2k >./simv |

If you want to dump a VCD file.

|

>Verilog2C++ UDIV64.v2k UDIV64 posedge CLK negedge RSTn dumpvars >g++ -O3 bench_dump.cc UDIV64.cc -o simc >./simc |

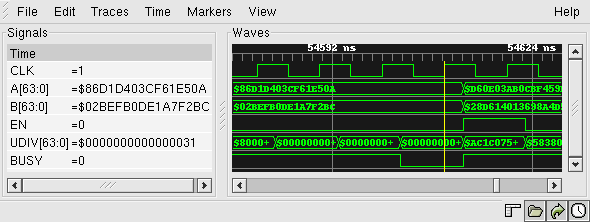

If you have a GTKWave.

|

>gtkwave dump.vcd UDIV64.tr |

-

....

-

....

-

I am planning to add these features for next version.

- Support for SystemVerilog

- SystemC and CycleC wapper

-

Verilog2C++ is written in C++ without any specific libraries and tools.

But, only tested on my system.

- linux 2.4.18 on x86

- gcc 3.2 20020903

- bison 1.35

- flex 2.5.4

- glibc 2.2.93

- libstdc++ 3.2 20020826

I have developped Verilog2C++ on tools shown below.